## Lesson 3

## Digitally-Controlled Single-Phase AC/DC Integrated PWM Converter

## **Goal of the work**

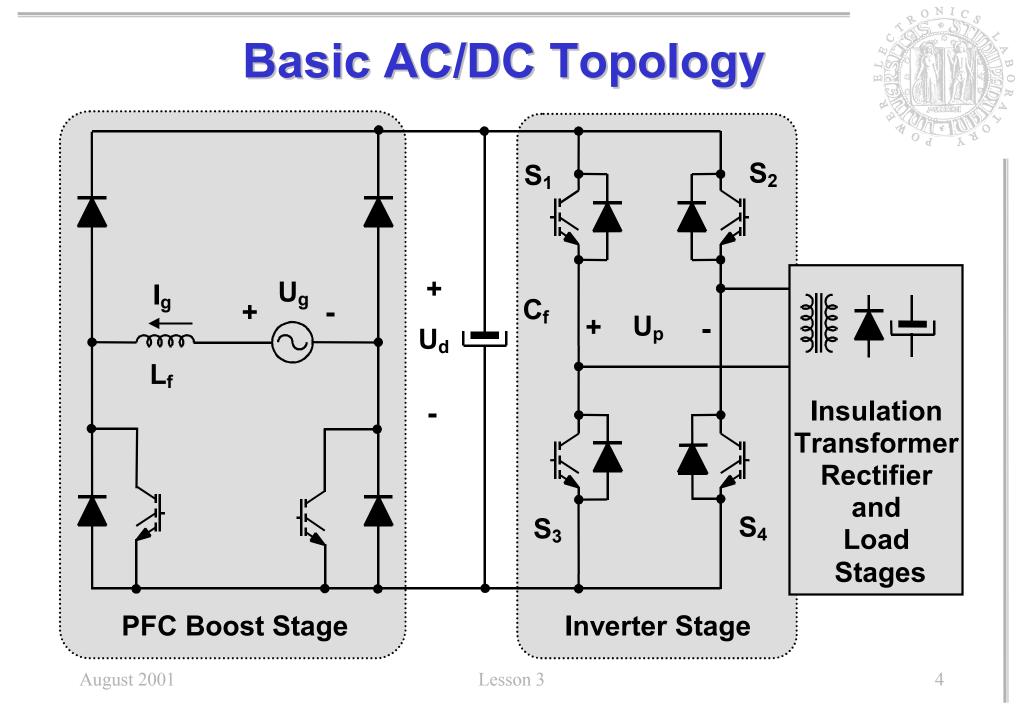

**Development of a new topology of single phase insulated ac/dc converter featuring:**

- high power factor

- full control of the output dc voltage

- high-frequency insulation transformer

- high-frequency line filter inductor.

## **Presentation Outline**

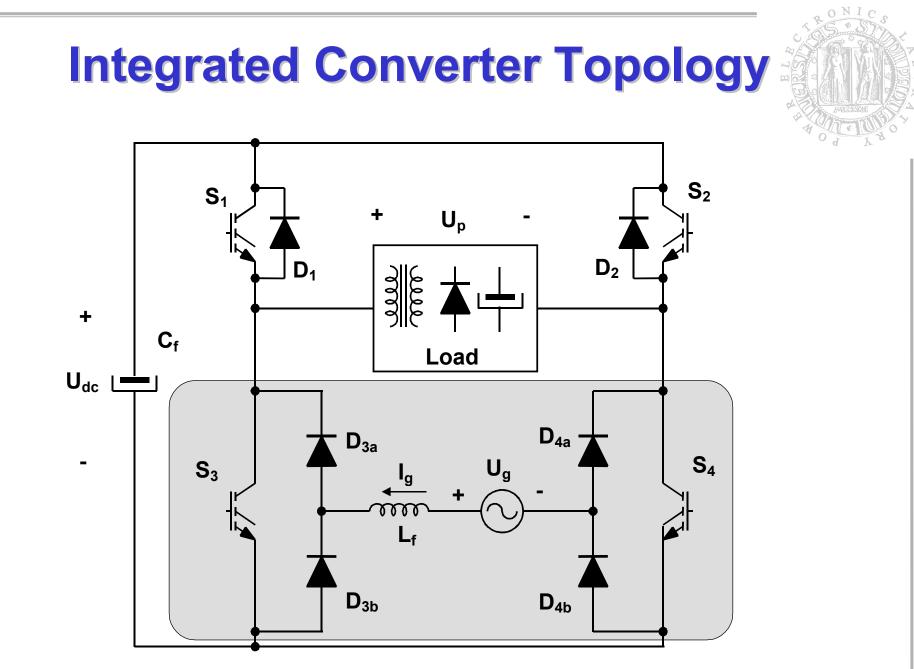

- Converter topology

- operation modes

- -structural constraints

- Design procedure

- Control strategy

- -analog control

- -digital control

- Experimental results

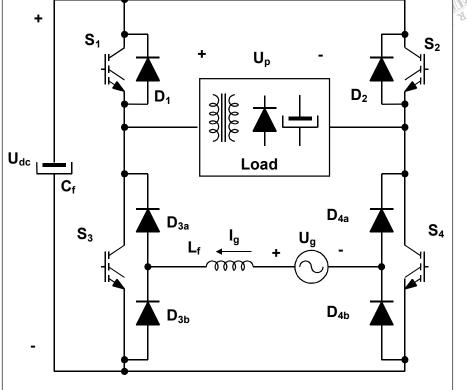

## **Converter Modes of Operation**

Switches are driven so as to generate powering and freewheeling phases.

Free-wheeling phases are obtained closing the two high-side or the two low-side switches.

The two free-wheeling phases have opposite effect on the converter input current thus allowing control of the current waveform.

#### The converter integrates the PFC and inverter stages but loses some degree of control. This limits the line (or load) side performance.

August 2001

## **Converter Operation Table**

| <b>Switches ON</b>                            | <b>Diodes ON</b>                                                           | Ug   | Up               | I <sub>g</sub> |

|-----------------------------------------------|----------------------------------------------------------------------------|------|------------------|----------------|

| <b>S</b> <sub>1</sub> - <b>S</b> <sub>2</sub> | $D_1, D_{3a}, D_{4b}$                                                      | > () | 0                | decrease       |

| <b>S</b> <sub>3</sub> - <b>S</b> <sub>4</sub> | <b>D</b> <sub>3a</sub> , <b>D</b> <sub>4b</sub>                            | > () | 0                | increase       |

| <b>S</b> <sub>1</sub> - <b>S</b> <sub>4</sub> | ( <b>D</b> <sub>1</sub> ), <b>D</b> <sub>3a</sub> , <b>D</b> <sub>4b</sub> | > () | +U <sub>dc</sub> | decrease       |

| <b>S</b> <sub>2</sub> - <b>S</b> <sub>3</sub> | $\mathbf{D}_{3a}, \mathbf{D}_{4b}$                                         | > () | -U <sub>dc</sub> | increase       |

| $S_1 - S_2$                                   | $D_2, D_{3b}, D_{4a}$                                                      | < () | 0                | increase       |

| <b>S</b> <sub>3</sub> - <b>S</b> <sub>4</sub> | <b>D</b> <sub>3b</sub> , <b>D</b> <sub>4a</sub>                            | < 0  | 0                | decrease       |

| <b>S</b> <sub>1</sub> - <b>S</b> <sub>4</sub> | $\mathbf{D}_{3b}, \mathbf{D}_{4a}$                                         | < () | +U <sub>dc</sub> | decrease       |

| <b>S</b> <sub>2</sub> - <b>S</b> <sub>3</sub> | ( <b>D</b> <sub>2</sub> ), <b>D</b> <sub>3b</sub> , <b>D</b> <sub>4a</sub> | < () | -U <sub>dc</sub> | increase       |

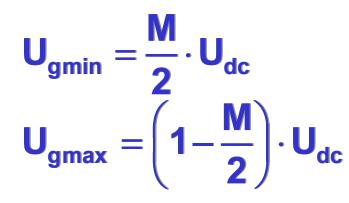

## **Operation Constraints**

- The duration of the powering phases must be the same to avoid output transformer saturation.

- The modulation period, T<sub>sw</sub>, is then divided into three phases:

- positive powering phase: duration M/2·T<sub>sw</sub>

- negative powering phase: duration M/2-T<sub>sw</sub>

- free-wheeling phase: duration (1 M)·T<sub>sw</sub>

- During the free-wheeling phase, input current control is possible.

When the modulation index M is high, the available time for the input current control is small.

The input current control is possible only when:

```

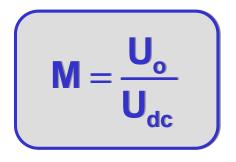

U_{gmin} < |U_g(\theta)| < U_{gmax}, where

```

# Average ac voltage at converter input and corresponding input current control angle **(**

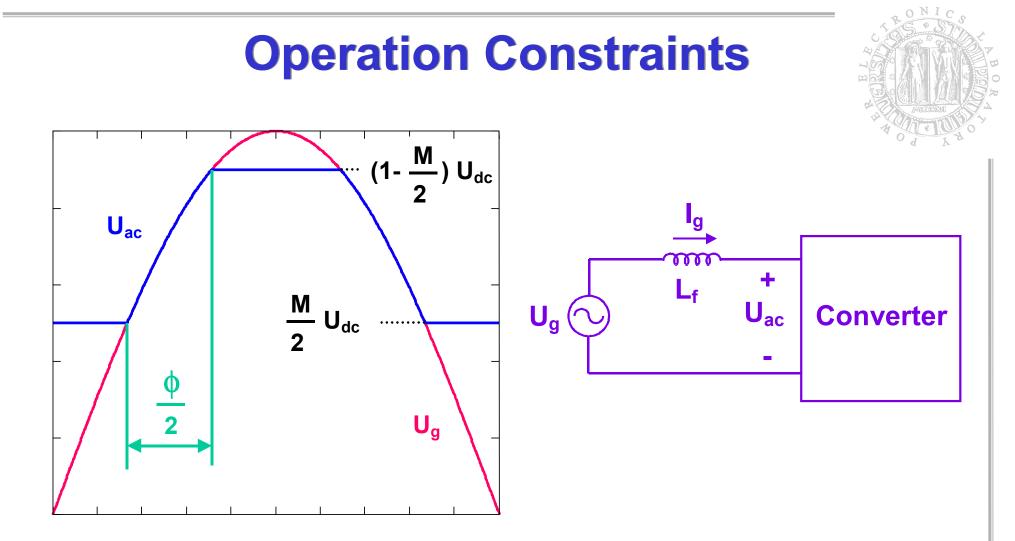

## **Operation Constraints**

Maximum allowed duty-cycle M and dc link voltage to peak input voltage ratio as a function of the line current control angle  $\phi$

## **Converter Design**

From the previous graphs the following design procedure can be adopted:

- Select maximum dc link voltage, based on switches' voltage rating;

- Given the peak line voltage, the design diagram allows to determine the maximum achievable M value;

- The same diagram also allows to determine the line control angle \$\ointy\$, that should be equal or higher than 120°, to get a satisfactory PF and current THD.

## **Converter Design**

#### **Passive components' selection:**

• Given the desired input current ripple, input inductance is given by:

$$L_{f} = \frac{U_{dc}}{4 \cdot f_{sw} \cdot \Delta I_{Lpp}} \qquad \qquad U_{dc} = dc \ link \ voltage$$

Given the desired low frequency output voltage ripple, the dc link capacitor can be selected according to:

$$\mathbf{C}_{f} = \frac{\mathbf{P}_{out}}{\mathbf{2} \cdot \pi \cdot \mathbf{f}_{line} \cdot \Delta \mathbf{U}_{dcpp} \cdot \mathbf{U}_{dc}}$$

## **Converter Design**

The maximum stresses for the active components are:

- Voltage stress equal to the DC link voltage

- Current stress for the upper switches as in any standard inverter

- Current stress for the lower switches and diodes is the sum of inverter load side and line side currents

## **Converter Control**

- We considered both an analog and a digital control technique.

- The analog solution is based on a standard PFC controller and on a modified phase-shift modulator for full-bridge converters.

- The digital solution is based on a dead-beat type of control equation and on a custom digital PWM modulator.

- In both cases the output voltage may be controlled by a standard regulator (e.g. PID).

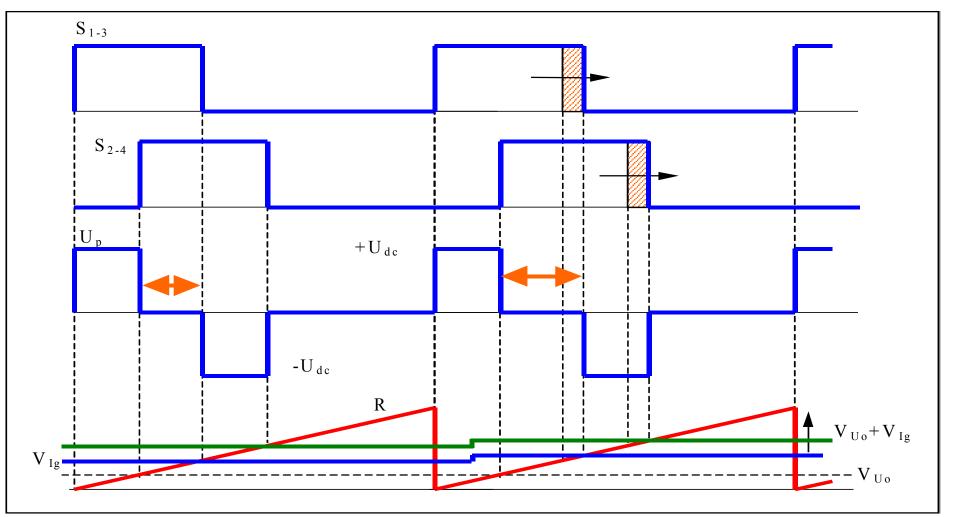

#### **Analog Converter Control Analog PWM S**<sub>1-3</sub> modulator S<sub>2-4</sub> Ramp // $S_{1-3}$ Up $C_1$ +U<sub>dc</sub> V<sub>Ig</sub> L 0 G $C_2$ Ι С S<sub>2-4</sub> $-U_{dc}$ $V_{\text{Uo}}$ $C_3$ Ramp V<sub>Uo</sub>+V<sub>Ig</sub> V<sub>Ig</sub> V<sub>Uo</sub> August 2001 Lesson 3 16

## **Analog Converter Control Control of the free-wheeling phase**

## **Analog Converter Control**

Symmetrical positioning of switching pulses requires two additional commutations

## **Analog Converter Control**

- The input variables of the PWM modulator, i.e. V<sub>Uo</sub> and V<sub>Ig</sub>, must be provided by the output voltage and input current regulators.

- The output voltage regulator may be any of those used for forward converters. A simple solution might be voltage mode control with PID regulator.

- The input current regulator may be a standard average current PFC controller with analog multiplier.

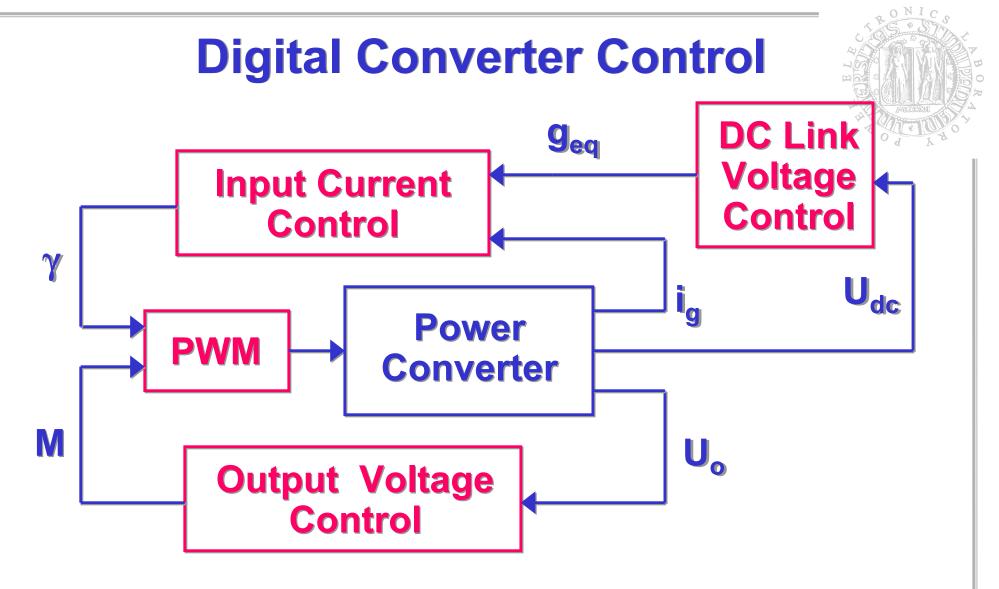

## **Digital Converter Control**

- Digital implementation requires significant computational power to allow input current, DC link voltage and output voltage control.

- Flexibility in the PWM modulator is required to implement the non-standard modulation strategy.

- Texas Instruments TMS320F240 DSP is the hardware platform selected for the practical implementation.

## **Digital Converter Control**

The control system is organized as follows:

- Digital PWM

- Input current control loop

- Output voltage control loop (not implemented)

- DC link voltage control loop

### **Digital control block diagram**

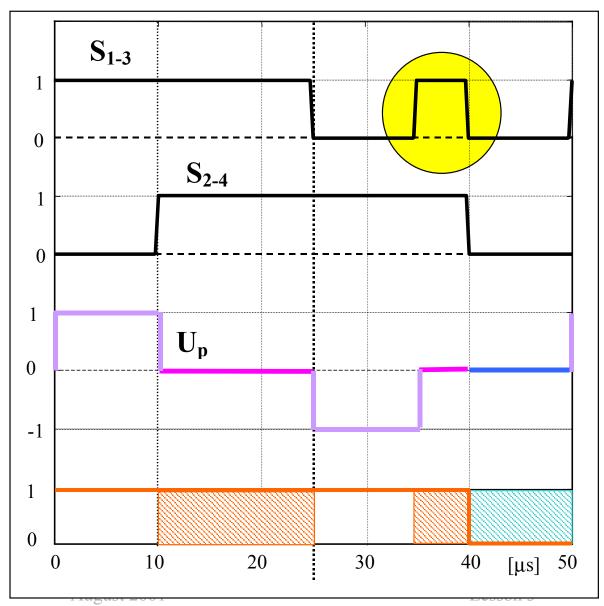

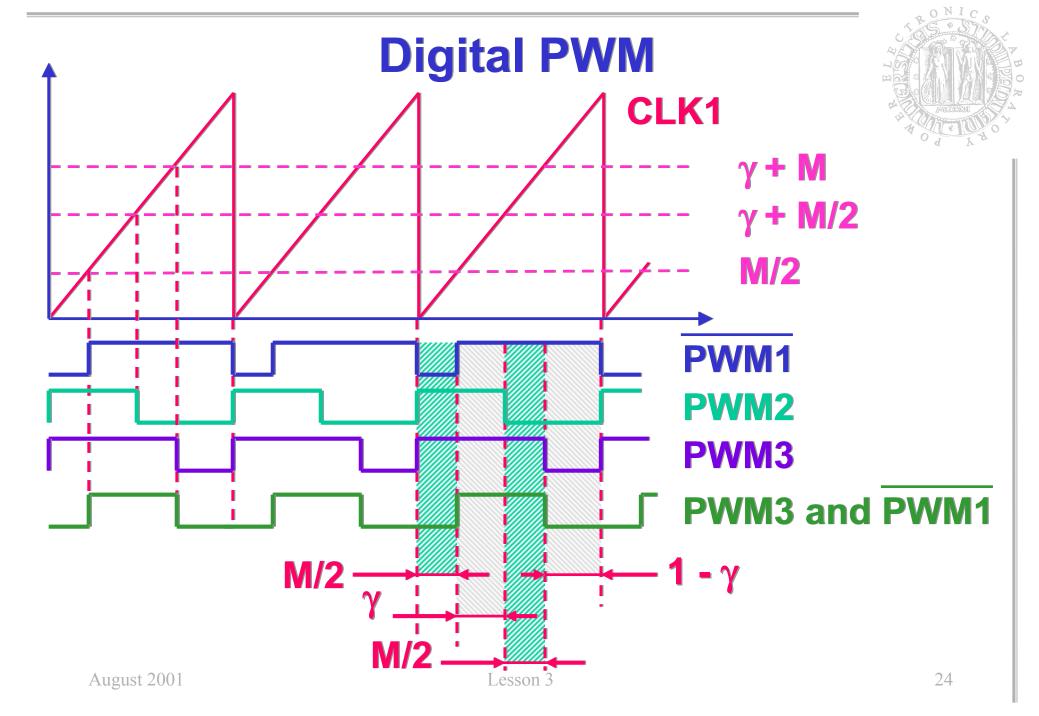

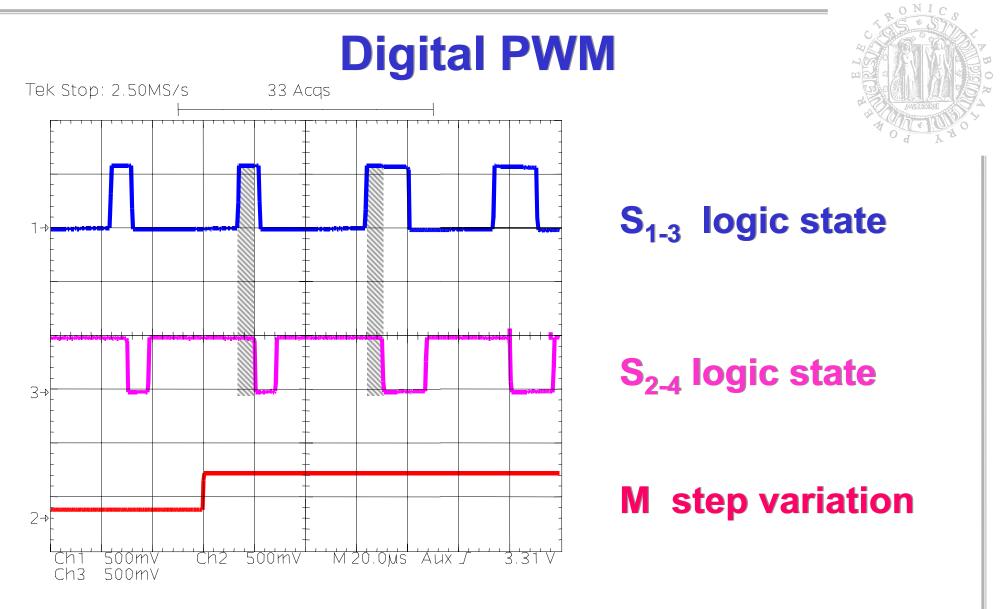

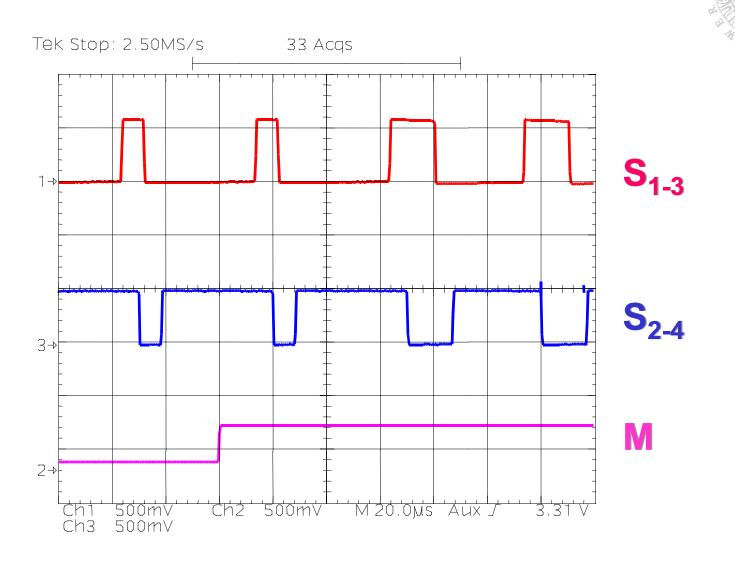

## **Digital PWM**

- The PWM implementation uses one of the three DSP internal counters. It is programmed for a period of 50 μs (20kHz).

- Three PWM outputs are used to generate the logic state of two inverter legs.

- The CMP input registers of the PWM units are loaded with values which are related to the load duty-cycle (M) and line "duty-cycle" γ.

- The duty-cycles are generated by external loops (output voltage and line current loops).

## **Digital PWM**

- This solution allows simultaneous and independent variation of the input variables.

- Its response time is equal to one modulation period (worst case).

- The constraint

$\gamma_{max} = 1 - M$

# requires the definition of a strategy to deal with the interactions between the two loops.

## **Digital PWM**

- The strategy we applied is to give the highest priority to the output voltage control loop.

- When the output voltage controller requires a sudden variation of the parameter M, this is performed even if input current control is lost.

- The input current controller must be capable of tolerating this momentary control losses without generating persisting oscillations and/or instabilities.

- These problems arise only in the presence of transients at the load side.

#### **Dynamic response of the PWM modulator**

August 2001

Lesson 3

• The input current dynamic equation is the following:

$$\mathbf{i}_{g}(\mathbf{t}) = \frac{1}{L_{f}} \cdot \int_{0}^{t} \mathbf{U}_{Lf}(\tau) d\tau = \frac{1}{L_{f}} \cdot \int_{0}^{t} \mathbf{U}_{g}(\tau) - \mathbf{U}_{ac}(\tau) d\tau$$

• This can be discretized by assuming the voltage to be constant between sampling instants (zero order hold discretization).

The input inductor average voltage in a modulation period can be easily found to be:

$$\mathbf{U}_{Lf} = \mathbf{U}_{g} - \mathbf{U}_{dc} \cdot [\mathbf{M}/2 + \delta \cdot (1 - \mathbf{M})]$$

Consequently, the current variation in a modulation period is given by:

$$i_{g}(k+1) - i_{g}(k) = U_{g}(k) \cdot \frac{T_{sw}}{L_{f}} + \left[ \frac{M}{2} + \delta(k) \cdot (1-M) \right] \cdot U_{dc}(k) \cdot \frac{T_{sw}}{L_{f}}$$

- The quantity  $\delta T_{sw}$  is the duration of the upper (or positive) free-wheeling phase.

- It is possible to calculate  $\delta(k+1)$  so as to force the current  $i_g$  to reach its reference at instant k+2.

- This generates the following control equation:

$$\begin{split} \delta(\mathbf{k}+\mathbf{1}) &= -\delta(\mathbf{k}) - \left[\mathbf{g}_{eq} \cdot \left|\mathbf{U}_{g}(\mathbf{k})\right| - \left|\mathbf{i}_{g}(\mathbf{k})\right|\right] \cdot \frac{\mathbf{L}_{f}}{\mathbf{T}_{sw} \cdot \mathbf{U}_{dc} \cdot (\mathbf{1}-\mathbf{M})} + \\ &+ \frac{2 \cdot \left|\mathbf{U}_{g}(\mathbf{k})\right|}{(\mathbf{1}-\mathbf{M}) \cdot \mathbf{U}_{dc}} - \frac{\mathbf{M}}{\mathbf{1}-\mathbf{M}}. \end{split}$$

The control equation assumes that

$$i_g(k+2) = g_{eq} \cdot U_g(k)$$

i.e.  $\mathbf{U}_{\mathbf{g}}$  is slowly varying with respect to the control period.

• G<sub>eq</sub> is the converter equivalent input conductance. This is generated by the DC link voltage control loop.

- The control equation is difficult to implement because it implies the execution of divisions.

- The variation of the DC link voltage can be neglected, i.e.  $U_{dc} \cong$  constant.

- The variation of M can be dealt with defining a new control variable:

$\gamma(\mathbf{k}) = [\mathbf{1} - \mathbf{M}(\mathbf{k})] \cdot \delta(\mathbf{k})$

- While  $\delta$  can vary from 0 to 1  $\gamma$  can vary from 0 to 1-M.

• This way, only MAC instructions can be used.

$$\begin{split} \gamma(\mathbf{k}+\mathbf{1}) &= -\gamma(\mathbf{k}) - \left[\mathbf{g}_{eq} \cdot \left|\mathbf{U}_{g}(\mathbf{k})\right| - \left|\mathbf{i}_{g}(\mathbf{k})\right|\right] \cdot \frac{\mathbf{L}_{f}}{\mathbf{T}_{sw} \cdot \mathbf{U}_{dc}} + \\ &+ \frac{2 \cdot \left|\mathbf{U}_{g}(\mathbf{k})\right|}{\mathbf{U}_{dc}} - \mathbf{M}(\mathbf{k}). \end{split}$$

• This is the implemented current control equation.

• The absolute value is required to deal with  $U_{\alpha} < 0$ .

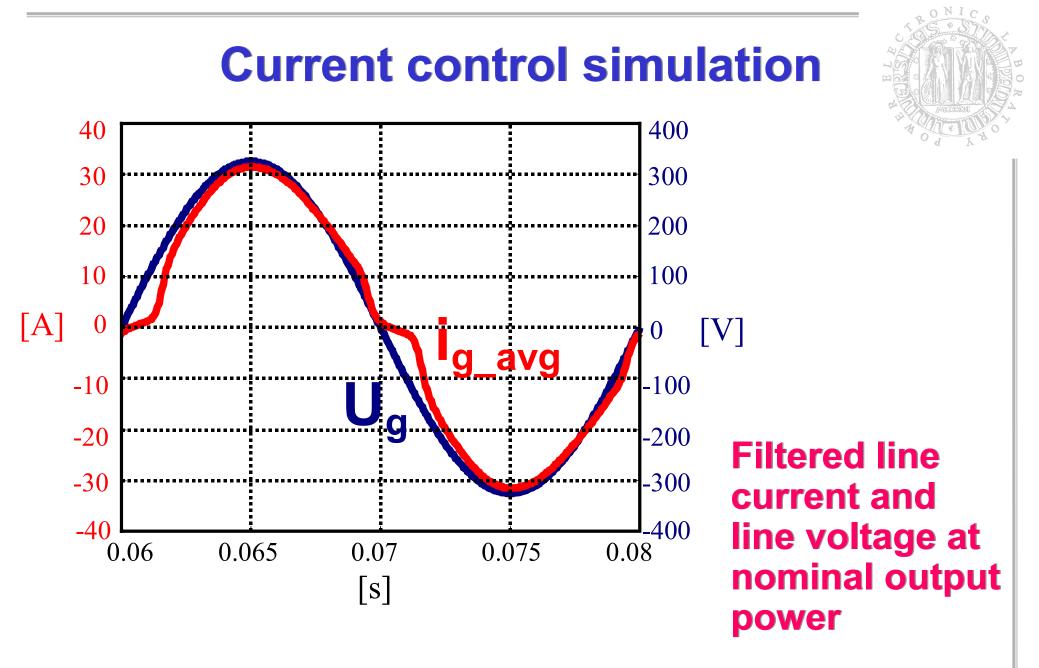

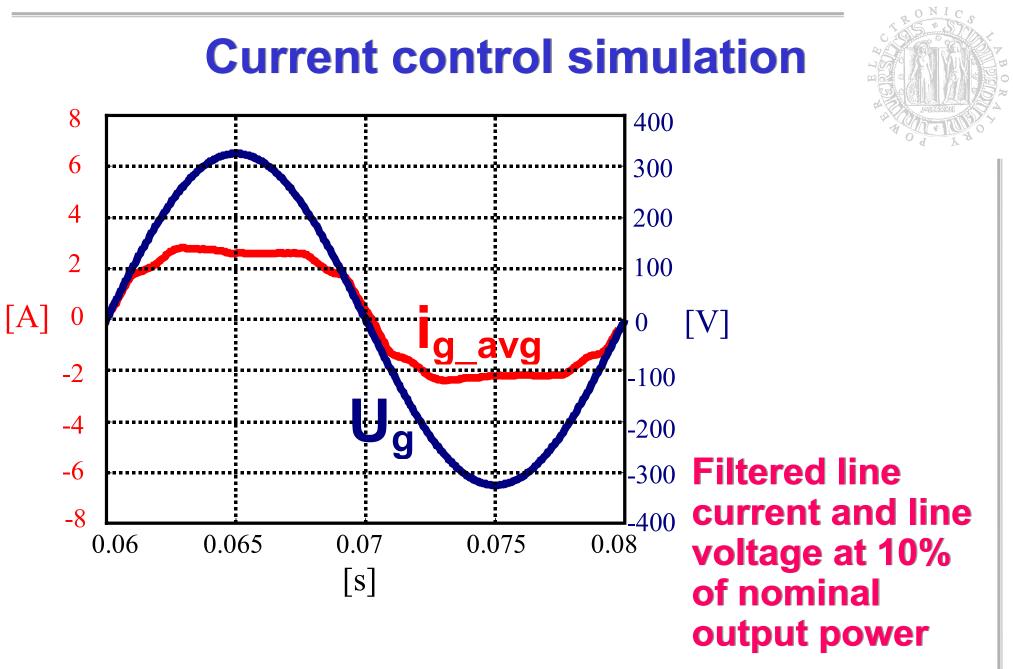

## **Current control simulation**

Simulation of the proposed input current digital control was performed.

## **Converter Parameters**

$240 \pm 10\% V_{RMS}$ Line voltage **Output power** 5 kW Switching frequency **kHz** f<sub>sw</sub> 20 Input inductor mH 1 L C<sub>f</sub> **DC** link capacitor 800 μF

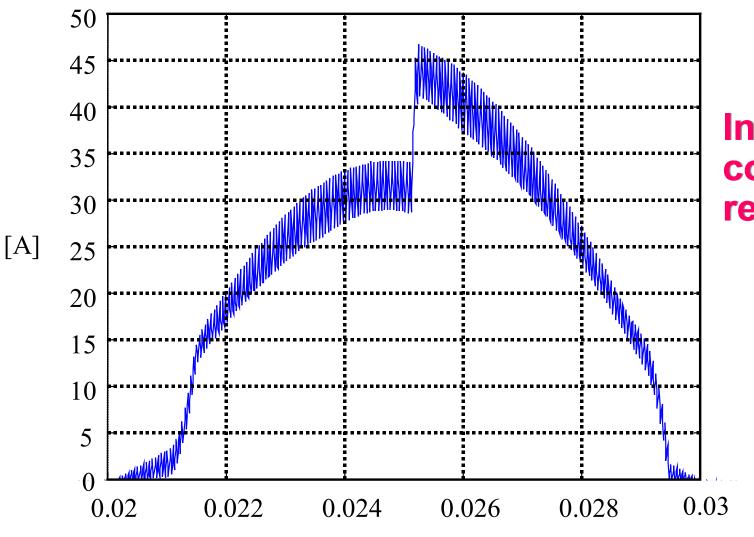

#### **Current control simulation** 40 35 30 Input current 25 [A] in a line half-20period 15 10 5 0.062 0.064 0.066 0.068 0.06 0.07 [S]

## **Current control simulation**

[s]

#### Input current control step response

## **DC link voltage control**

- The DC link voltage control can be implemented quite straightforwardly.

- It is a simple PI regulator designed on the equivalent load resistance and DC link capacitor, as in any conventional PFC.

- The bandwidth is limited to 10 15 Hz to avoid input current distortion.

- Sampling frequency can be reduced accordingly. In our implementation we used 1 kHz.

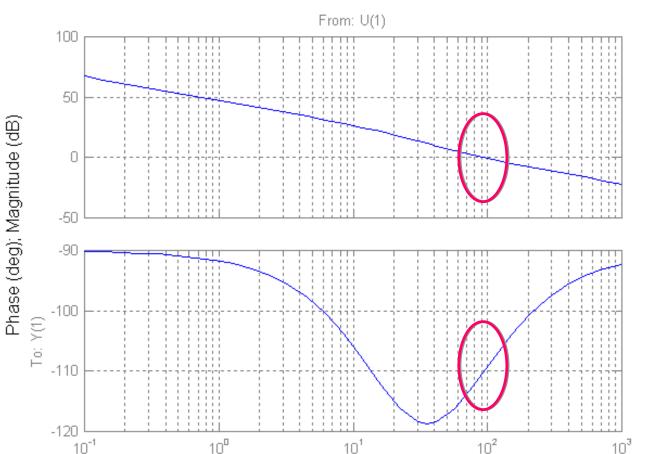

## **DC link voltage control**

Frequency (rad/sec)

Tu

Open loop gain Bode plot.  $F_{cr} = 15Hz$  $m_f = 70^{\circ}$

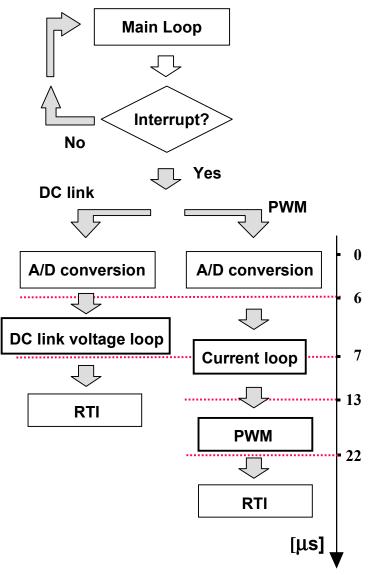

## **Control implementation**

- The DC link voltage control routine is performed at 1 kHz sampling frequency. It requires 7 μs, including A/D conversion.

- The PWM routine, including the line current controller, is instead executed at 20 kHz.

This requires 22 μs, again including A/D conversion.

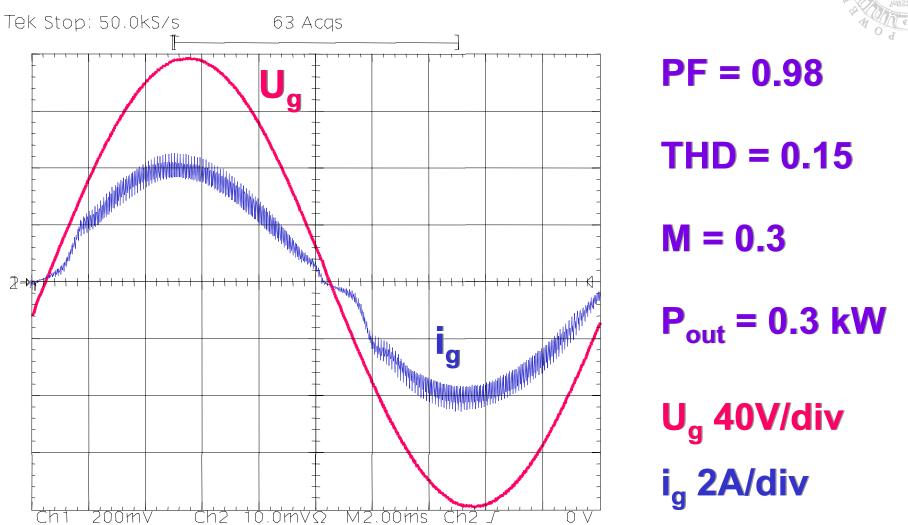

## **PWM implementation**

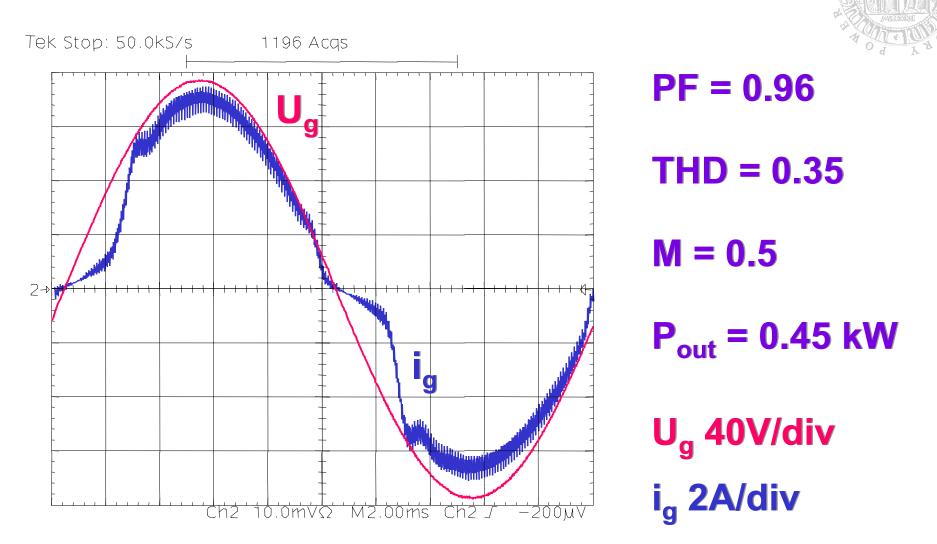

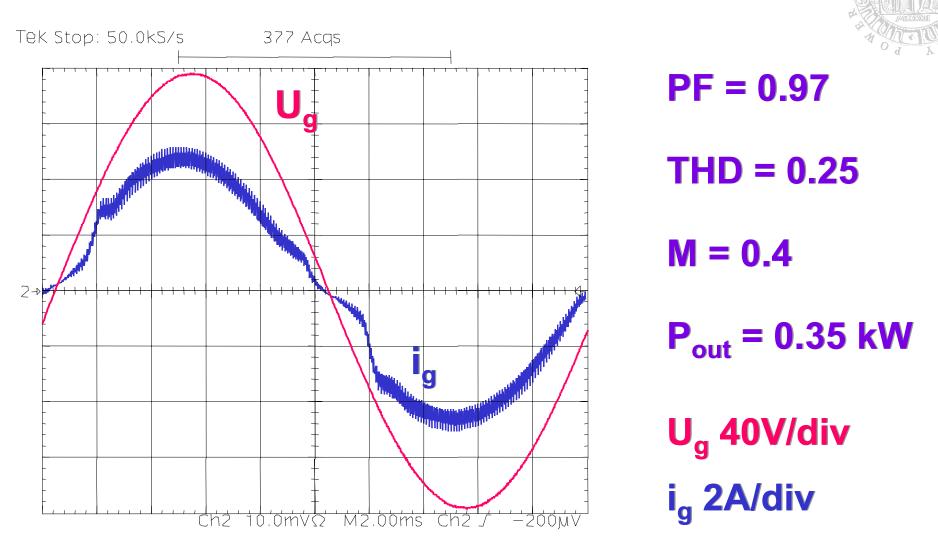

A prototype of the proposed converter was built to test the digital controller.

### **Converter Parameters**

$110 \pm 10\% V_{RMS}$ Line voltage **Output power** 0.5 P<sub>o</sub> kW Switching frequency f<sub>sw</sub> 20 **kHz** Input inductor 1.8 mH L C<sub>f</sub> **DC** link capacitor 500 μF

## Reference

L. Rossetto, S. Buso: "Digitally-Controlled Single-Phase AC/DC Integrated PWM Converter", IEEE IAS Annual Meeting 2001, in press.